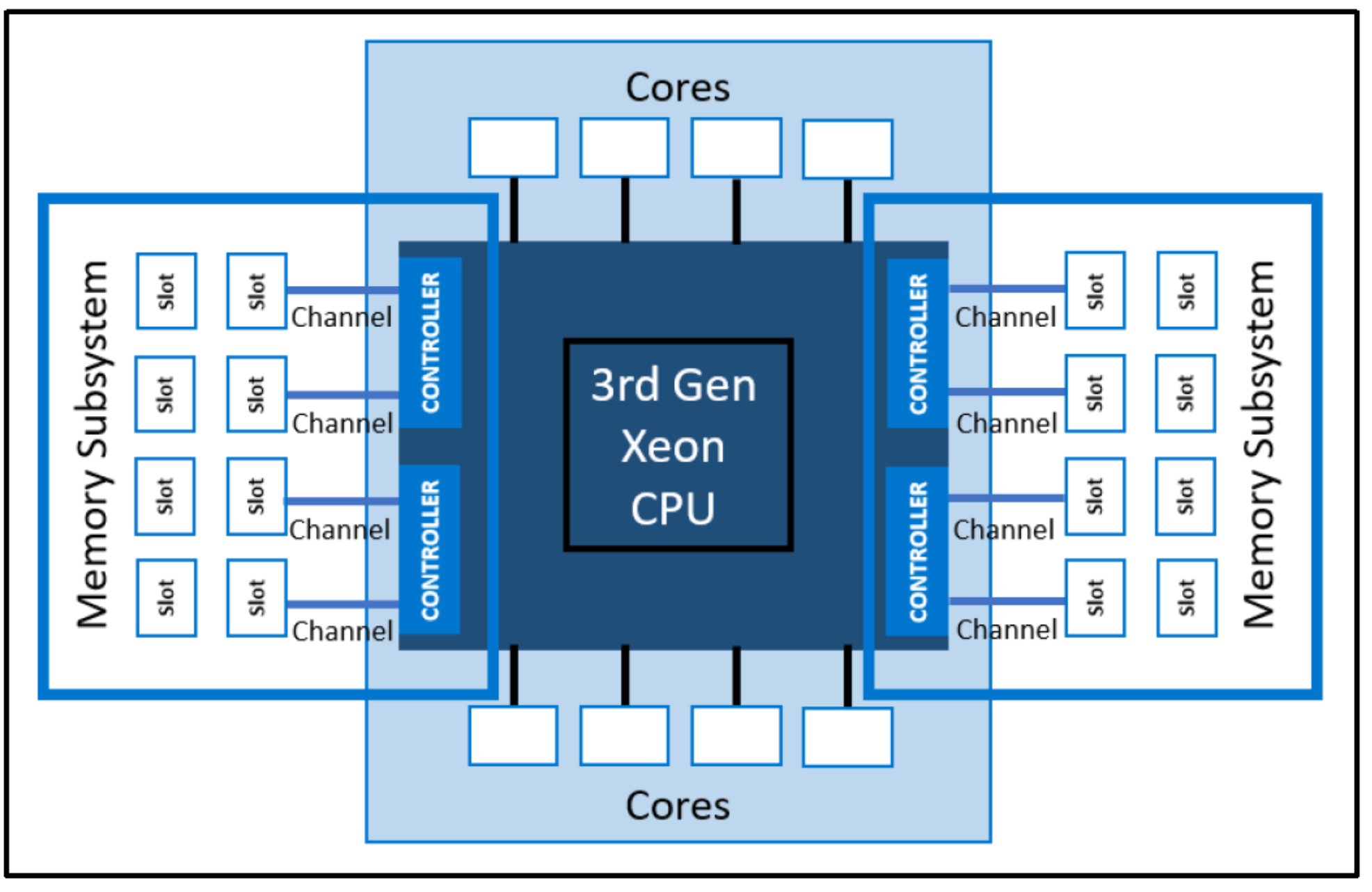

NanoMesh Core, separated into the compute (CPU) subsystem and memory... | Download Scientific Diagram

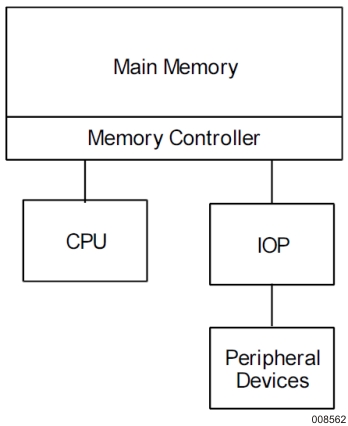

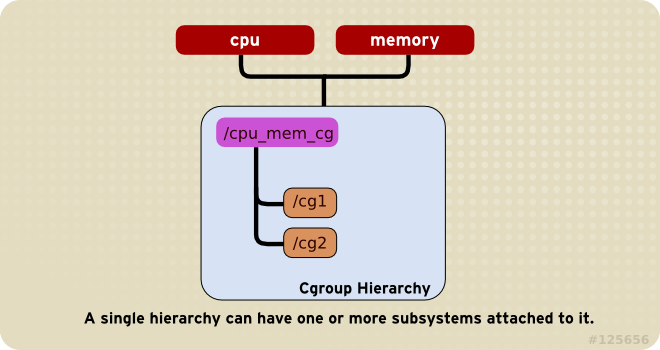

1.2. Relationships Between Subsystems, Hierarchies, Control Groups and Tasks Red Hat Enterprise Linux 6 | Red Hat Customer Portal

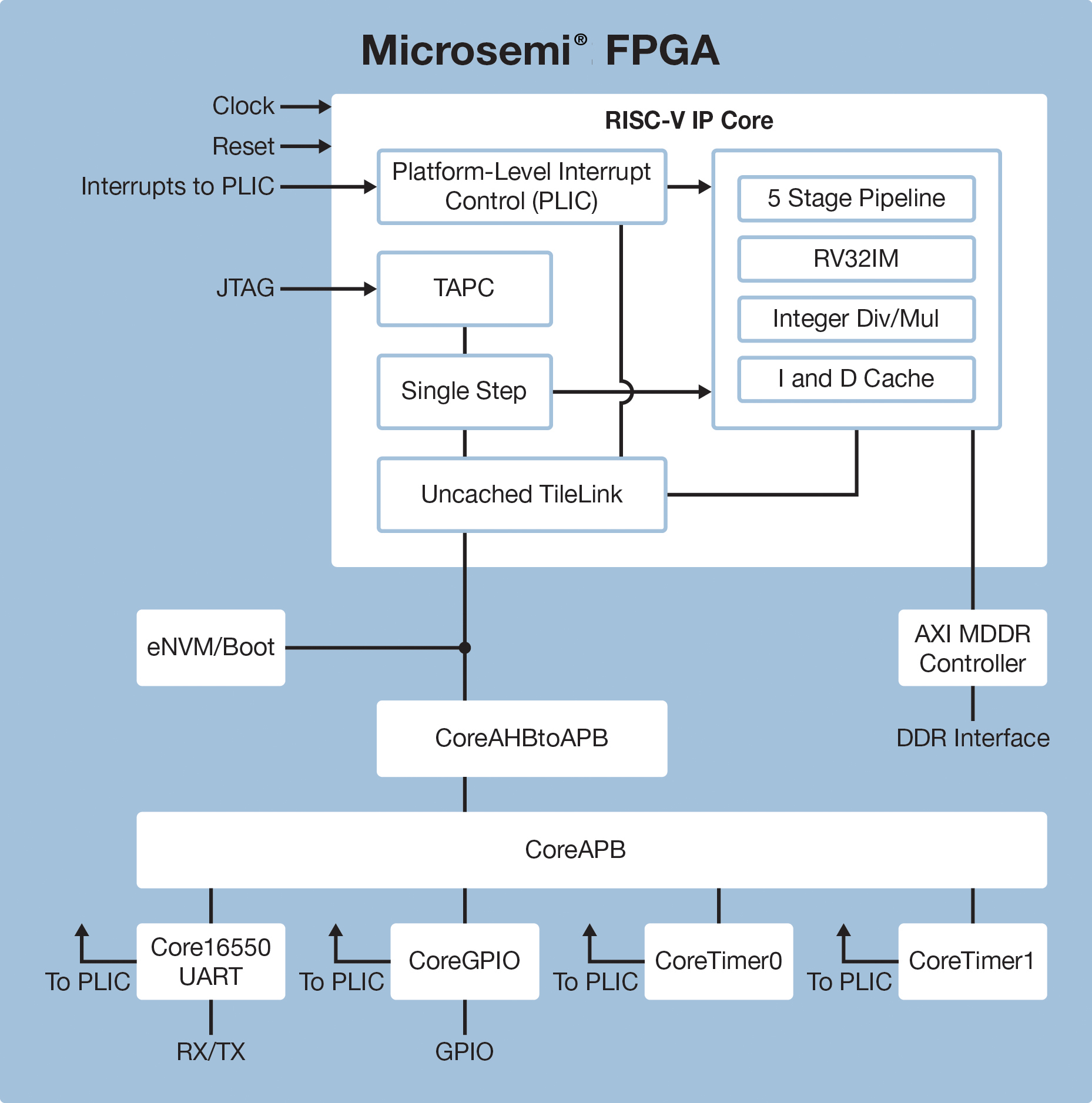

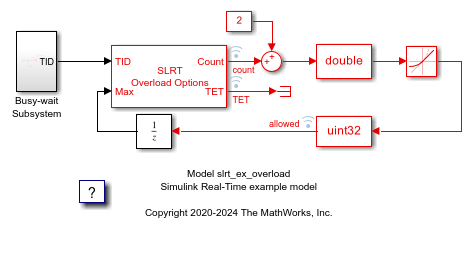

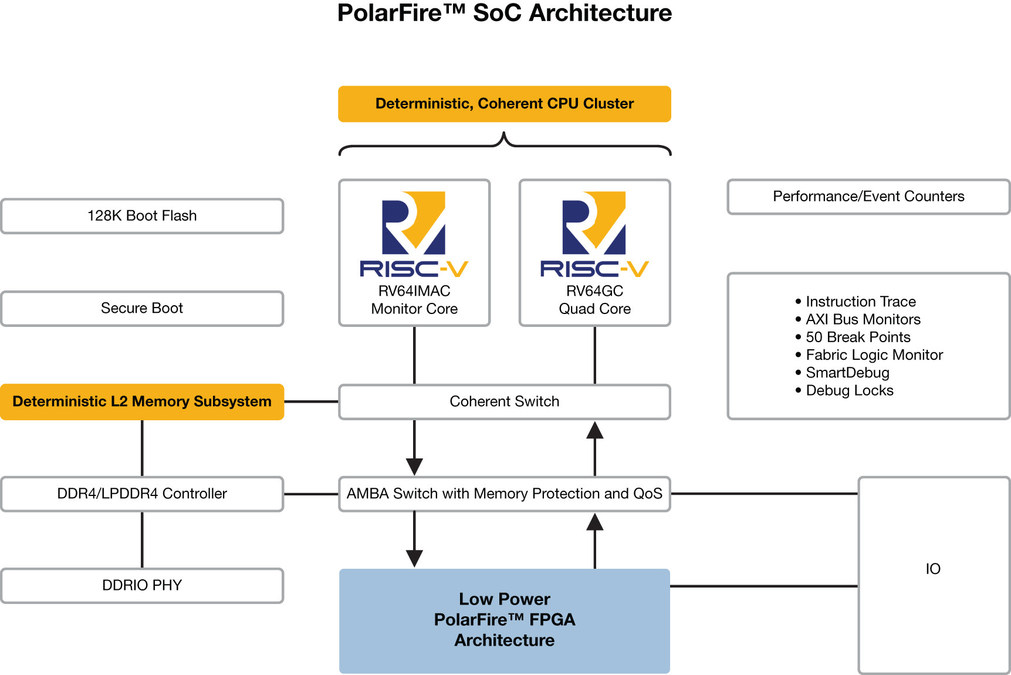

Industry's First RISC-V SoC FPGA Architecture Brings Real-Time to Linux, Giving Developers the Freedom to Innovate in Low-Power, Secure and Reliable Designs

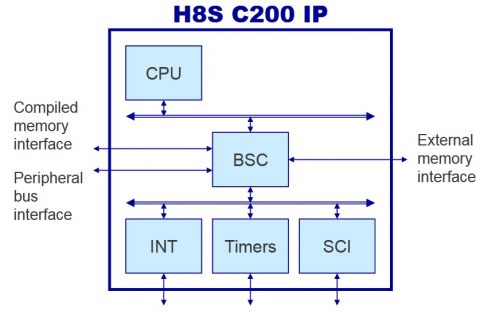

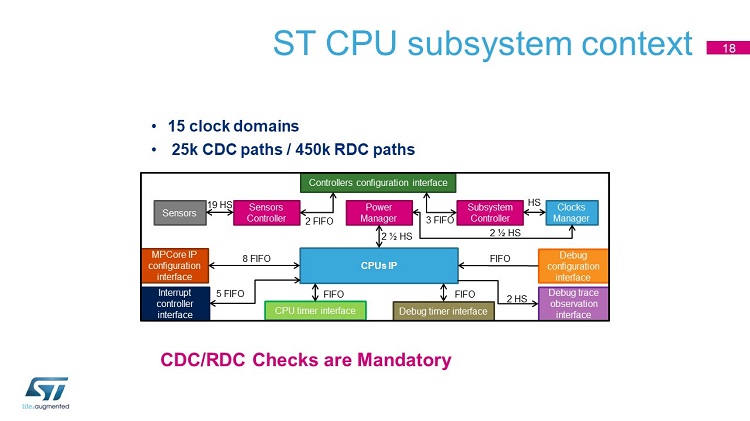

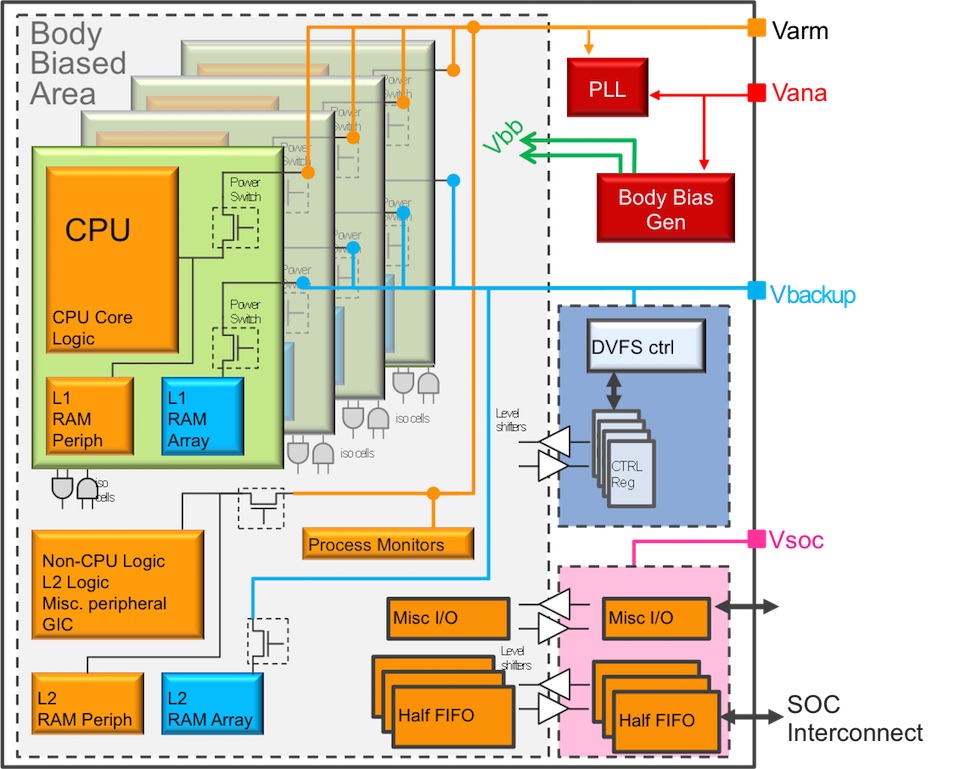

![PDF] Implementation and Verification of a CPU Subsystem for Multimode RF Transceivers | Semantic Scholar PDF] Implementation and Verification of a CPU Subsystem for Multimode RF Transceivers | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/998a554518f21a201f10daf6698b9e7fc3ed546a/16-Figure2.1-1.png)

PDF] Implementation and Verification of a CPU Subsystem for Multimode RF Transceivers | Semantic Scholar

NanoMesh Core, separated into the compute (CPU) subsystem and memory... | Download Scientific Diagram

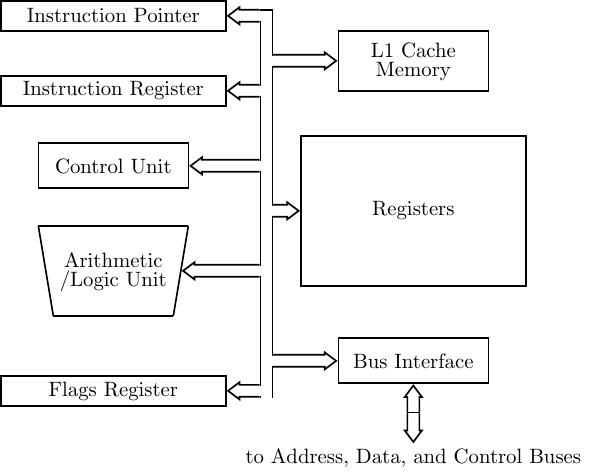

Figure 3 from Using abstract CPU subsystem simulation model for high level HW/SW architecture exploration | Semantic Scholar